Codeur prioritaire

Un codeur 2^n: n ne fonctionne correctement que si aucune des entrées ou une seule entrée n'est au niveau logique 1. Lorsque plusieurs entrées prennent simultanément le niveau logique 1, le codage est erroné. Une solution, dans ce cas, consiste à utiliser un encodeur prioritaire.

Un encodeur prioritaire génère un code binaire correspondant au numéro de l'entrée active ayant la priorité la plus élevée (ou, le plus souvent, le nombre le plus élevé). Il peut être utilisé dans les applications suivantes:

- codeur clavier: lorsque plusieurs touches sont enfoncées simultanément, seule la touche avec le numéro le plus élevé est prise en compte;

- unité de traitement des demandes d'interruption dans un microprocesseur: en cas de demandes d'interruption simultanées, seule la demande de priorité la plus élevée est acceptée.

Codeur prioritaire 4 : 2

La table de vérité pour un encodeur de priorité 4: 2 est donnée dans le tableau 3.19, où x représente un état sans importance. Pour un mot d'entrée, le bit actif avec le poids le plus élevé est prioritaire

Les cartes de Karnaugh présentées dans les figures 3.25–3.27 sont

construites en supposant que chaque état indifférent peut prendre le niveau

logique 0 ou le niveau logique 1.

Les équations logiques résultantes peuvent être écrites comme suit:

Le circuit logique du codeur de priorité 4: 2 peut alors être réalisé comme illustré sur la figure 3.28.

|

| Figure 3.28: Codeur prioritaire 4: 2 avec sortie de validation |

Les codeurs de priorité proposés par les fabricants de circuits intégrés disposent d'entrées et de sorties supplémentaires (entrée d'activation, EI, sortie d'activation, E0, sortie de signal de groupe, GS ou V) qui peuvent être nécessaires pour les connexions en cascade.

La transcription de ces équations à l'aide de portes logiques aboutit au circuit représenté sur la figure 3.33 (a). La Figure 3.33 (b) représente le symbole d'un codeur de priorité 4: 2 avec capacité de cascade. Le codeur de priorité 8: 3 illustré à la Figure 3.33 (c) est implémenté par la mise en cascade de deux codeurs de priorité 4: 2.

|

| Figure 3.33. Circuit a) et symbole b) pour un codeur de priorité 4: 2 avec capacité de mise en cascade; c) 8: 3 codeur prioritaire |

Cela met en jeu les expressions logiques suivantes:

Codeur prioritaire 10: 4

Un codeur de priorité 10: 4 ou un codeur de priorité binaire décimale effectue le codage des niveaux logiques d'entrée de telle sorte que seule une modification du niveau logique de l'entrée de rang le plus élevé est prise en considération.

Comme le zéro décimal ou D0 correspond au cas où toutes les entrées sont au niveau logique bas, l'entrée D0 est omise. L'entrée Di, avec i étant un nombre compris entre 1 et 9, ne peut activer la sortie Yj (j = 0, 1, 2, 3) que si aucune entrée de priorité supérieure et autre que celles qui activent également Yj prend la niveau logique haute

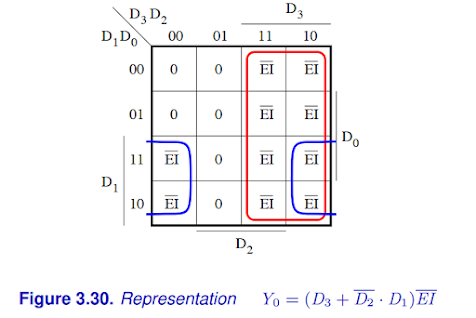

Sur la base de la table de conversion présentée dans le tableau 3.22, il est possible de formuler une proposition logique pour chaque sortie. Ainsi, la sortie Y0 prend le niveau logique haut lorsque l'une des conditions suivantes est vraie:

D1 est au niveau logique haut, et D2, D4, D6 et D8 sont au niveau logique bas;

D3 est au niveau logique haut, et D4, D6 et D8 sont au niveau logique bas;

D5 est au niveau logique haut, et D6 et D8 sont au niveau logique bas;

D7 est au niveau logique haut et D8 est au niveau logique bas;

D7 est au niveau logique haut;

Cela se traduit par:

Tableau 3.22. Conversion de nombres décimaux de 0 à 9 en représentation binaire

La figure 3.34 représente le circuit logique du codeur de priorité 74LS147. Pour ce type de circuit, les entrées et sorties sont actives au niveau logique bas. La table de vérité du tableau 3.23 montre que la priorité de chaque entrée est déterminée par son rang en décimal.

Chaque entrée active n'est prise en compte que si, et seulement si, toutes les entrées de rang supérieur sont inactives.

Figure 3.34. Codeur de priorité 10: 4 (circuit intégré 74LS147)

Tableau 3.23. Table de vérité pour le codeur prioritaire 74LS147

Post a Comment